# **Poseidon User Manual**

# EPIC format VIA CPU Board with Integrated Data Acquisition

7463010 v1.4

© Copyright 2010

1255 Terra Bella Ave. Mountain View, CA 94043 Tel (650) 810-2500 Fax (650) 810-2525 www.diamondsystems.com

# **Table of Contents**

| Introduction                                                             | 7  |

|--------------------------------------------------------------------------|----|

| Description and Features                                                 | 7  |

| Block Diagram                                                            |    |

| Functional Overview                                                      |    |

| Board Description                                                        | 13 |

| Connector Summary                                                        | 14 |

| Jumper Summary                                                           | 14 |

| Connectors                                                               | 15 |

| PC/104 ISA Bus                                                           | 15 |

| PC/104-Plus PCI Bus                                                      | 16 |

| PS2 Mouse and Keyboard connector                                         | 17 |

| Utility Connector                                                        |    |

| Data Acquisition (Digital I/O) Connector                                 |    |

| Data Acquisition (Analog I/O) Connector                                  | 20 |

| Ethernet Connector                                                       |    |

| Audio I/O Connector                                                      |    |

| Speaker Connector                                                        |    |

| External Auxiliary Power Connector (Output)                              |    |

| IDE Connector                                                            |    |

| Serial Port I/O Connector                                                |    |

| External Battery Connector                                               |    |

| LCD Panel (LVDS Interface) Connector<br>VGA Connector                    |    |

| LCD Backlight Connector                                                  |    |

| Power Input Connector                                                    |    |

| USB 2.0 Connectors                                                       |    |

| Serial ATA Connector                                                     |    |

| I/O Panel Power                                                          |    |

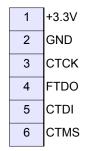

| Standard JTAG Configuration Interface (Factory Use)                      |    |

| Reference Voltage Test Point (Factory Use)                               |    |

| Board Configuration                                                      | 25 |

| •                                                                        |    |

| Power Configuration Options                                              |    |

| PCI VI/O Voltage Setting (JP1)                                           |    |

| DAQ Configuration (JP2)                                                  |    |

| COM3/COM4/ADC IRQ Configuration (JP3)                                    |    |

| Analog I/O Single-ended/Differential Configuration (JP4)                 |    |

| DAC Configuration (JP5)                                                  |    |

| Battery Connection (JP6)                                                 |    |

| ATX Power Control (JP7)<br>RS-422/RS-485 Termination Configuration (JP8) |    |

|                                                                          |    |

| DIO Pull-up/Pull-down Configuration (JP9)                                |    |

| System Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| System Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45       |

| Console Redirection to a Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Backup Battery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| System Reset<br>On-Board Video                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47       |

| System I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48       |

| Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48       |

| Serial Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| PS/2 Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| USB Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49       |

| Data Acquisition Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51       |

| Data Acquisition Circuitry I/O Map                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52       |

| I/O Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| I/O Register Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56       |

| Enabling Enhanced Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77       |

| Enhanced Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| Normal Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| Analog-to-Digital Input Ranges and Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78       |

| Analog-to-Digital Input Ranges and Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| Overview<br>Unipolar and Bipolar Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78<br>78 |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| Overview<br>Unipolar and Bipolar Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br>Performing an A/D Conversion                                                                                                                                                                                                                                                                                                                                                               |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br>Performing an A/D Conversion<br>Select the Input Channel<br>Select the Input Range                                                                                                                                                                                                                                                                                                         |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br><b>Performing an A/D Conversion.</b><br>Select the Input Channel<br>Select the Input Channel<br>Wait for Analog Input Circuit to Settle                                                                                                                                                                                                                                                    |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br><b>Performing an A/D Conversion.</b><br>Select the Input Channel<br>Select the Input Channel<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel.                                                                                                                                                                                               |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br><b>Performing an A/D Conversion.</b><br>Select the Input Channel<br>Select the Input Channel<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish                                                                                                                                                           |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br><b>Performing an A/D Conversion.</b><br>Select the Input Channel<br>Select the Input Channel<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish<br>Read the Data from the Board                                                                                                                           |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br><b>Performing an A/D Conversion.</b><br>Select the Input Channel<br>Select the Input Channel<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish                                                                                                                                                           |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br><b>Performing an A/D Conversion.</b><br>Select the Input Channel<br>Select the Input Channel<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish<br>Read the Data from the Board                                                                                                                           |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br>Performing an A/D Conversion<br>Select the Input Channel<br>Select the Input Range<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish<br>Read the Data from the Board<br>Convert the numerical data to a meaningful value<br>Sampling Methods<br>Sampling Modes                                           |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br>Performing an A/D Conversion<br>Select the Input Channel<br>Select the Input Range<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish<br>Read the Data from the Board<br>Convert the numerical data to a meaningful value<br>A/D Sampling Methods<br>Sampling Modes<br>FIFO Description                   |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br>Performing an A/D Conversion<br>Select the Input Channel<br>Select the Input Range<br>Wait for Analog Input Circuit to Settle.<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish<br>Read the Data from the Board<br>Convert the numerical data to a meaningful value<br>A/D Sampling Methods<br>Sampling Modes<br>FIFO Description<br>Scan Sampling |          |

| Overview<br>Unipolar and Bipolar Inputs<br>Input Ranges and Resolutions<br>A/D Conversion Formulas<br>Performing an A/D Conversion<br>Select the Input Channel<br>Select the Input Range<br>Wait for Analog Input Circuit to Settle<br>Perform an A/D Conversion on the Current Channel<br>Wait for the Conversion to Finish<br>Read the Data from the Board<br>Convert the numerical data to a meaningful value<br>A/D Sampling Methods<br>Sampling Modes<br>FIFO Description                   |          |

| Analog Output Ranges and Resolution                                           | 87  |

|-------------------------------------------------------------------------------|-----|

| Description                                                                   | 87  |

| Resolution                                                                    |     |

| Full-scale Range Selection                                                    | 87  |

| Digital-to-Analog Conversion                                                  | 88  |

| Compute the D/A Output Value for the Desired Output Voltage                   | 88  |

| Compute the LSB and MSB Values                                                |     |

| Add the Channel Number to the MSB                                             |     |

| Set D/A Simultaneous Update Bit<br>Write the LSB and MSB to the Board         |     |

| Monitor the DACBUSY Status Bit                                                |     |

|                                                                               |     |

| Waveform Generator                                                            |     |

| Description                                                                   |     |

| Programming the D/A Waveform Generator                                        | 91  |

| Auto-calibration                                                              |     |

| Background                                                                    |     |

| Performing Auto-calibration with Software                                     |     |

| Performing Auto-calibration with dsPIC                                        | 94  |

| Digital I/O Operation                                                         | 95  |

| Main Digital I/O Internal 82C55 Circuit                                       | 95  |

| Auxiliary Digital I/O                                                         | 96  |

| Counter/Timer Operation                                                       | 98  |

| Counter/Timer Features and Configuration Options                              |     |

| Counter/Timer Configuration                                                   |     |

| Counter/Timer Access and Programming                                          | 98  |

| Watchdog Timer Programming                                                    | 99  |

| FlashDisk Module                                                              | 101 |

|                                                                               |     |

| Installing the FlashDisk Module<br>Using the FlashDisk with Another IDE Drive |     |

| Power Supply                                                                  |     |

| FlashDisk Programmer Board                                                    | 103 |

| I/O Cables                                                                    | 104 |

| Mounting PC/104-Plus Cards onto a Poseidon Baseboard                          | 105 |

|                                                                               |     |

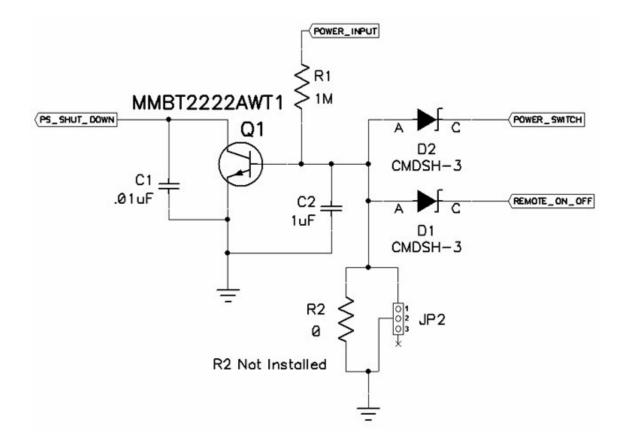

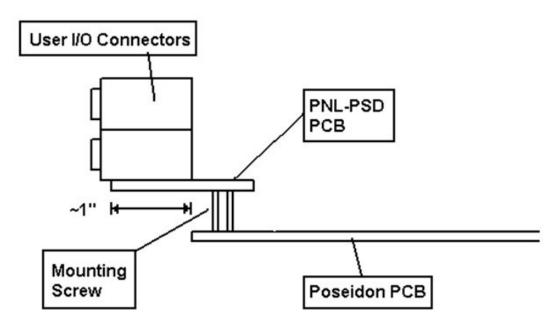

| PNL-PSD Panel I/O Board for Poseidon CPU                                      | 105 |

| Specifications                                               | 114            |

|--------------------------------------------------------------|----------------|

| CPU                                                          | 114            |

| Data Acquisition Circuitry                                   | 114            |

| Power Supply                                                 | 115            |

| General                                                      | 115            |

| Additional Information                                       | 116            |

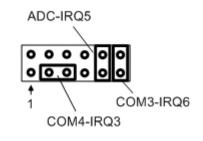

| Appendix A. COM3/4/ADC IRQ Configuration for First Release I | Boards, Rev A1 |

|                                                              |                |

| Technical Support                                            | 118            |

# Figures

| Figure 1: Poseidon Functional Block Diagram                           | 9  |

|-----------------------------------------------------------------------|----|

| Figure 2: Poseidon Board Layout                                       | 13 |

| Figure 3: CN6 and CN7 Connectors                                      | 15 |

| Figure 4: CN3 Connector                                               | 16 |

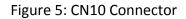

| Figure 5: CN10 Connector                                              | 23 |

| Figure 6: CN8 Connector                                               | 27 |

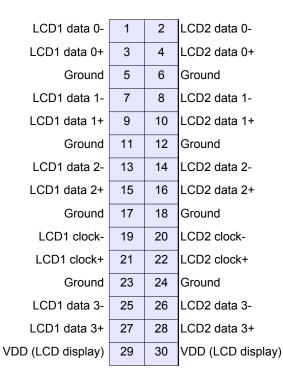

| Figure 7: LCD Panel Connector                                         | 28 |

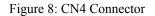

| Figure 8: CN4 Connector                                               | 30 |

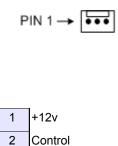

| Figure 9: CN9 Connector                                               | 30 |

| Figure 10: Serial ATA Connector                                       | 32 |

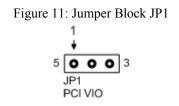

| Figure 11: Jumper Block JP1                                           | 35 |

| Figure 12: JP1 Settings                                               | 36 |

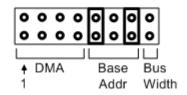

| Figure 13: Base Address Configuration Example                         | 37 |

| Figure 14: DMA Channel Selection                                      | 37 |

| Figure 15: Bus Width Configuration                                    | 38 |

| Figure 16: IRQ Selection Example                                      | 39 |

| Figure 17: Analog I/O Single-ended/Differential Configuration Example | 40 |

| Figure 18: JP5 Jumper Block                                 | 40  |

|-------------------------------------------------------------|-----|

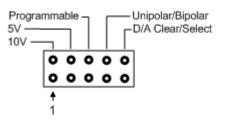

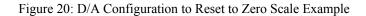

| Figure 19: D/A Configuration for ±5V Output Range Example   | 41  |

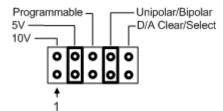

| Figure 20: D/A Configuration to Reset to Zero Scale Example | 41  |

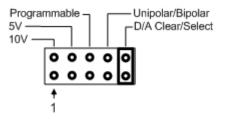

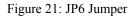

| Figure 21: JP6 Jumper                                       | 41  |

| Figure 22: ATX Configuration Using JP7                      | 42  |

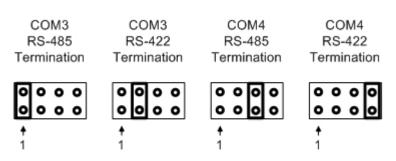

| Figure 23: RS-422/RS-485 Termination Configuration Options  | 43  |

| Figure 24: DIO Pull-up/Pull-down Configuration              | 43  |

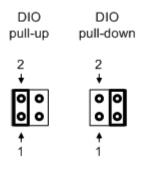

| Figure 25: Data Acquisition Block Diagram                   |     |

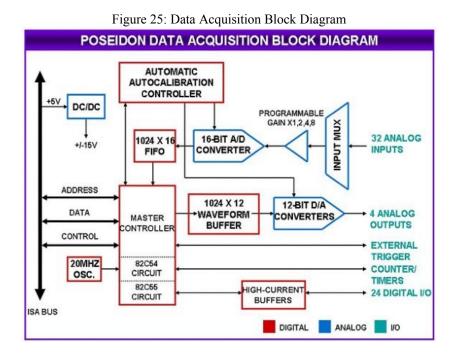

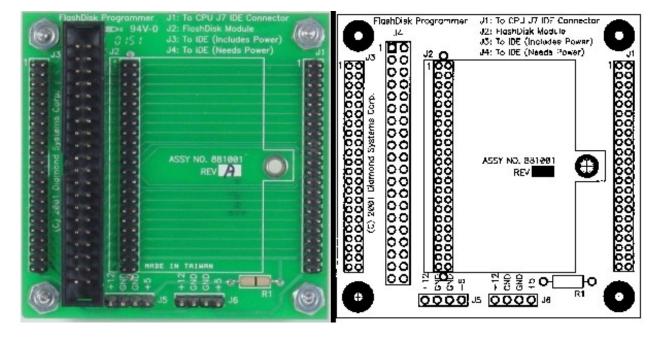

| Figure 26: FlashDisk Module                                 | 100 |

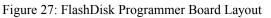

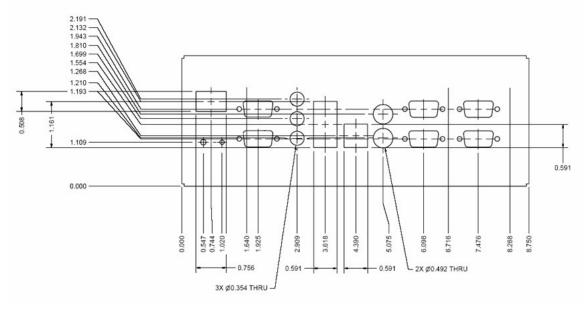

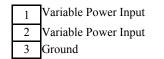

| Figure 27: FlashDisk Programmer Board Layout                | 102 |

# Introduction

Poseidon is an embedded single board computer (SBC) in an EPIC form factor that integrates CPU and data acquisition circuitry into a single board.

Poseidon conforms to the EPIC standard with expansion support via PC/104-*Plus*, an embedded standard that is based on the ISA and PCI buses and provides a compact, rugged mechanical design for embedded systems. PC/104 modules feature a pin and socket connection system in place of card edge connectors, as well as mounting holes for stand-offs in each corner. The result is an extremely rugged computer system fit for mobile and miniature applications. PC/104 modules stack together with 0.6" spacing between boards (0.662" pitch including the thickness of the PCB).

Poseidon uses the PCI bus internally to connect the Ethernet circuit to the processor. It uses the ISA bus internally to connect serial ports 3 and 4, as well as the data acquisition circuit, to the processor. Both the ISA and PCI buses are brought out to expansion connectors for the connection of add-on boards. Diamond Systems manufactures a wide variety of compatible PC/104 add-on boards for analog I/O, digital I/O, counter/timer functions, serial ports, and power supplies.

# **Description and Features**

The Poseidon board is an all-in-one embedded SBC with the following key system and data acquisition features.

#### Processor Section

- Low-power, fanless 1.0GHz VIA Eden ULV CPU or high-performance 2.0GHz VIA C7 CPU.

- 512MB or 1GB 533MHz DDR2 RAM soldered, on-board, system memory.

- 400MHz front side bus.

- 2MB 16-bit wide integrated flash memory for BIOS and user programs.

- Advanced 2D/3D graphics engine with integral MPEG-2 hardware acceleration.

- 33MHz PCI Bus.

#### I/O Section

- 4 serial ports, 115.2kbaud max.

- 2 ports 16550-compatible

- 2 ports 16850-compatible with 128-byte FIFOs and RS-232, RS-422 and RS-485 capability, with RS-422/485 termination.

- 4 USB 2.0 ports.

- Accepts solid-state IDE FlashDisk modules directly on board.

- 10-/100-/1000BaseT Gigabit Ethernet.

- CRT and 24-bit dual channel LVDS flat panel support.

- Dual Independent Display.

- PS/2 keyboard and mouse ports.

- S-ATA and UDMA-100 IDE interfaces.

- Interface for amplified audio.

#### Analog Input

- 32 single-ended/16 differential inputs, 16-bit resolution.

- 250KHz maximum aggregate A/D sampling rate.

- Bipolar input ranges: ±10V, ±5V, ±2.5V, ±1.25V, ±0.625V.

- Unipolar input ranges: 0-10V, 0-5V, 0-2.5V, 0-1.25V, 0-.625V.

- 5 ppm/°C drift accuracy.

- Internal and external A/D triggering.

- 1024-sample FIFO for reliable high-speed sampling and scan operation.

#### Analog Output

- 4 analog outputs, 12-bit resolution.

- $\pm 5V, \pm 10V, 0-5V, 0-10V$  output ranges available.

- Simultaneous update.

- Adjustable output range (optional).

#### Digital I/O

- 24 programmable digital I/O lines, 3.3V and 5V logic compatible.

- Enhanced output current capability: +64/-15mA max.

- Selectable pull-up/down resistors on board.

#### *Counter/Timers*

- 1 24-bit counter/timer for A/D sampling rate control.

- 1 16-bit counter/timer for user counting and timing functions.

- Programmable gate and count enable.

- Internal and external clocking capability.

#### System Features

- Plug and play BIOS with IDE auto detection, 32-bit IDE access, and LBA support.

- User-selectable COM1 or COM2 terminal mode.

- On-board lithium backup battery for real-time-clock and CMOS RAM.

- ATX power switching capability.

- Programmable watchdog timer.

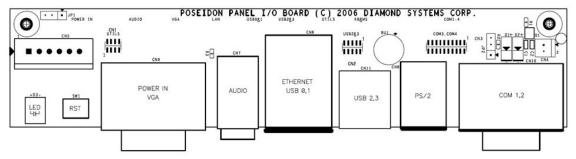

- I/O panel board that connects to on-board I/O brought to pin headers, to provide PC-style connectors.

- Power supply: 5VDC operation from the PC-104 bus.

# **Block Diagram**

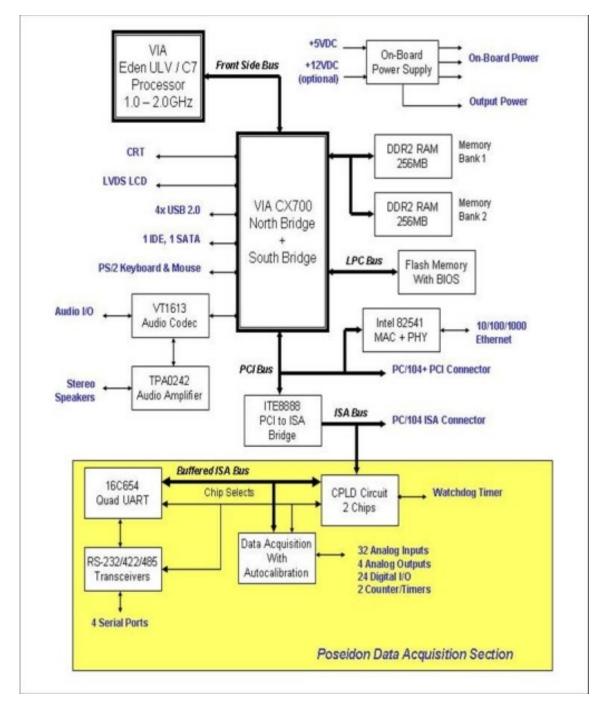

Figure 1 shows the Poseidon functional blocks.

Figure 1: Poseidon Functional Block Diagram

# **Functional Overview**

This section describes the major Poseidon subsystems.

#### Processor

Two processor options are available for the Poseidon board.

- Low-power, fanless 1.0GHz VIA Eden ULV CPU

- High-performance 2.0GHz VIA C7 CPU

#### North Bridge and South Bridge

The North and South bridge are integrated in the on-board VIA CX700 chip.

#### Memory

The board accommodates 512MB or 1GB of SDRAM system memory soldered on the board. No expansion connector is provided for additional memory.

The board also includes flash memory for storage of BIOS and user programs. Flash memory is accessible via the on-board ISA bus.

#### Video Features

Video circuitry is provided by the VIA CX700 chipset and includes,

- Dual 200MHz 2D/3D graphics engines featuring dedicated 128-bit data paths for pixel data flow and texture/command access.

- An integrated MPEG-2 decoder.

- Dual independent display with separate frame buffers for CRT and flat panel displays.

#### Audio

The design provides AC97 audio support derived from the South Bridge chip. The Via VT1612A CODEC provides audio processing. Give special attention to design and routing to minimize noise on the audio I/O lines.

Audio I/O includes,

- Stereo line in.

- Stereo line out.

- Mono mic in.

- Stereo internal line in.

The board includes audio power amplifier circuitry for stereo speaker output. The amplifier circuit is powered by +5VDC from the board. User DC control of volume is also provided, which overrides the software settings.

#### Ethernet

The board supports 10-/100-/1000BaseT (Gigabit) Ethernet. Magnetics are included on the board so that a complete circuit is provided.

# Data Acquisition

| Type of I/O    | Characteristics                                                                                                              |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------|--|

| Analog Input   | 32 single-ended/16 differential inputs,16-bit resolution                                                                     |  |

| Analog Output  | Four analog outputs, 12-bit resolution                                                                                       |  |

| Digital I/O    | 24 programmable digital I/O, 3.3V and 5V logic compatible                                                                    |  |

| Counter/Timers | One 24-bit counter/timer for A/D sampling rate control<br>One 16-bit counter/timer for user counting and timing<br>functions |  |

The board provides the following data acquisition capabilities.

#### Standard Peripherals

The board provides the following standard system peripherals.

| Peripheral   | Characteristics                                      |  |

|--------------|------------------------------------------------------|--|

| Serial ports | Four serial ports                                    |  |

| PS/2 ports   | Keyboard and mouse                                   |  |

| USB ports    | Four USB 2.0 function ports                          |  |

| IDE ports    | One 44-pin connector for HDD or FlashDisk            |  |

|              | Compact flash socket                                 |  |

|              | One standard S-ATA connector for up to two S-ATA HDD |  |

Serial ports 3 and 4 can be BIOS-selected for RS-232, RS-485 or RS-422. Termination resistors of 120 ohms can be jumper-enabled on these two ports.

Console redirection feature is incorporated. This feature enables keyboard input and character video output to be routed to one of the serial ports.

The board contains provision for mounting a solid state IDE flashdisk module with capacities ranging from 32MB and greater. The module mounts onto the board using a 44-pin 2mm pitch header and a hold-down mounting hole with spacer and screws.

#### **Bus Interfaces**

The PCI bus is the primary connection between the North/South bridge, Ethernet, and PC/104-Plus devices.

The ISA bus is exposed on PC/104 connectors for use by add-on modules. The PC/104-*Plus* connectors allow expansion above the board only.

#### Power Supply

The power supply is an on-board converter, allowing an input range of +5VDC,  $\pm5\%$ . Jumper selection allows power to be taken from the PC-104 bus and not from the on-board converter.

The power supply includes ATX power switching and ACPI power management support. The master +5V input is controlled by the ATX function with an external switch input.

# Battery Backup

The board includes a backup battery for CMOS RAM and real-time clock backup. The battery life is greater than four years. A connector and jumper are provided to disable the on-board battery and enable the use of an external battery, instead.

#### Watchdog Timer

A watchdog timer (WDT) circuit consists of a programmable timer.

# **Board Description**

#### Board Layout

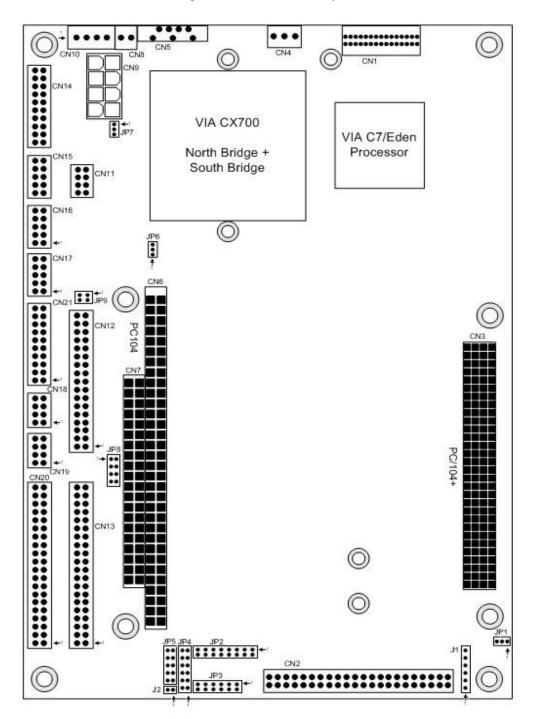

Figure 2 shows the Poseidon board layout, including connectors, jumper blocks and mounting holes.

# **Connector Summary**

The following table lists the connectors on the Poseidon board.

| Connector | Description                                | Manufacturer Part No.      |

|-----------|--------------------------------------------|----------------------------|

| CN1       | LCD panel (LVDS interface)                 | JST: BM30B-SRDS-G-TF       |

| CN2       | Primary IDE                                | Standard 2x22, 0.1" header |

| CN3       | PC/104-Plus PCI bus connector              | EPT 264-60303-02           |

| CN4       | LCD backlight                              | TYCO 640456-3              |

| CN5       | Serial ATA                                 | CATCH SATA-75              |

| CN6       | PC/104, ISA bus A,B                        | EPT 962-40323-03           |

| CN7       | PC/104, ISA bus C,D                        | EPT 962-40203-03           |

| CN8       | External battery                           | TYCO 640456-2              |

| CN9       | Input Power                                | Molex 39-31-0088           |

| CN10      | External auxiliary power (output)          | TYCO 640456-4              |

| CN11      | Speaker                                    | Standard 2x4, 2mm header   |

| CN12      | Data acquisition digital I/O, 34-pin       | Standard 2x17, 2mm header  |

| CN13      | Data acquisition analog I/O, 40-pin        | Standard 2x20, 2mm header  |

| CN14      | I/O panel power                            | Standard 2x10, 2mm header  |

| CN15      | Audio I/O                                  | Standard 2x5, 2mm header   |

| CN16      | VGA                                        | Standard 2x5, 2mm header   |

| CN17      | Ethernet                                   | Standard 2x5, 2mm header   |

| CN18      | Standard button/LED utility connector      | Standard 2x4, 2mm header   |

| CN19      | PS/2 Mouse and keyboard                    | Standard 2x4, 2mm header   |

| CN20      | RS-232/RS-485/RS-422 serial I/O (COM1-4)   | Standard 2x20, 2mm header  |

| CN21      | USB 0/1, USB 2/3 (USB 2.0)                 | Standard 2x10, 2mm header  |

| J1        | Standard JTAG interface (Factory use)      | -                          |

| J2        | Voltage reference test point (Factory use) | -                          |

|           |                                            |                            |

# Jumper Summary

The following table lists the jumpers on the Poseidon board.

| Jumper | Description                             |

|--------|-----------------------------------------|

| JP1    | PCI voltage selection                   |

| JP2    | DAQ configuration                       |

| JP3    | COM3/4 and DAQ IRQ selection            |

| JP4    | DAQ single-ended/differential selection |

| JP5    | DAC range configuration                 |

| JP6    | Battery power selection                 |

| JP7    | ATX power                               |

| JP8    | RS-422/485 termination                  |

| JP9    | DIO pull-up/pull-down configuration     |

# Connectors

This section describes the on-board Poseidon connectors.

#### PC/104 ISA Bus

Connectors CN6 and CN7 carry the ISA bus signals. Figure 3 shows the PC/104 A and B pin layout for CN6, and the C and D pin layout for CN7.

| Figure 3: CN6 and CN7 Co | onnectors |     |

|--------------------------|-----------|-----|

| A1 A32                   | C0        | C19 |

| B1 B32                   | D0        | D19 |

| CN6 Connector Pinout |     |     |          |

|----------------------|-----|-----|----------|

| IOCHCHK-             | A1  | B1  | GND      |

| SD7                  | A2  | B2  | RESETDRV |

| SD6                  | A3  | B3  | +5V      |

| SD5                  | A4  | B4  | IRQ9     |

| SD4                  | A5  | B5  | -5V      |

| SD3                  | A6  | B6  | DRQ2     |

| SD2                  | A7  | B7  | -12V     |

| SD1                  | A8  | B8  | ENDXFR-  |

| SD0                  | A9  | B9  | +12V     |

| IOCHRDY              | A10 | B10 | keyed    |

| AEN                  | A11 | B11 | SMEMW-   |

| SA19                 | A12 | B12 | SMEMR-   |

| SA18                 | A13 | B13 | IOW-     |

| SA17                 | A14 | B14 | IOR-     |

| SA16                 | A15 | B15 | DACK3-   |

| SA15                 | A16 | B16 | DRQ3     |

| SA14                 | A17 | B17 | DACK1-   |

| SA13                 | A18 | B18 | DRQ1     |

| SA12                 | A19 | B19 | REFRESH- |

| SA11                 | A20 | B20 | SYSCLK   |

| SA10                 | A21 | B21 | IRQ7     |

| SA9                  | A22 | B22 | IRQ6     |

| SA8                  | A23 | B23 | IRQ5     |

| SA7                  | A24 | B24 | IRQ4     |

| SA6                  | A25 | B25 | IRQ3     |

| SA5                  | A26 | B26 | DACK2-   |

| SA4                  | A27 | B27 | TC       |

| SA3                  | A28 | B28 | BALE     |

| SA2                  | A29 | B29 | +5V      |

| SA1                  | A30 | B30 | OSC      |

| SA0                  | A31 | B31 | GND      |

| GND                  | A32 | B32 | GND      |

| <b>CN7</b> Connector Pinout |     |     |         |  |  |  |  |  |  |

|-----------------------------|-----|-----|---------|--|--|--|--|--|--|

| GND                         | D0  | D0  | GND     |  |  |  |  |  |  |

| SBHE-                       | D1  | D1  | MEMCS16 |  |  |  |  |  |  |

| LA23                        | D2  | D2  | IOCS16- |  |  |  |  |  |  |

| LA22                        | D3  | D3  | IRQ10   |  |  |  |  |  |  |

| LA21                        | D4  | D4  | IRQ11   |  |  |  |  |  |  |

| LA20                        | D5  | D5  | IRQ12   |  |  |  |  |  |  |

| LA19                        | D6  | D6  | IRQ15   |  |  |  |  |  |  |

| LA18                        | D7  | D7  | IRQ14   |  |  |  |  |  |  |

| LA17                        | D8  | D8  | DACK0-  |  |  |  |  |  |  |

| MEMR-                       | D9  | D9  | DRQ0    |  |  |  |  |  |  |

| MEMW-                       | D10 | D10 | DACK5-  |  |  |  |  |  |  |

| SD8                         | D11 | D11 | DRQ5    |  |  |  |  |  |  |

| SD9                         | D12 | D12 | DACK6-  |  |  |  |  |  |  |

| SD10                        | D13 | D13 | DRQ6    |  |  |  |  |  |  |

| SD11                        | D14 | D14 | DACK7-  |  |  |  |  |  |  |

| SD12                        | D15 | D15 | DRQ7    |  |  |  |  |  |  |

| SD13                        | D16 | D16 | +5      |  |  |  |  |  |  |

| SD14                        | D17 | D17 | MASTER- |  |  |  |  |  |  |

| SD15                        | D18 | D18 | GND     |  |  |  |  |  |  |

| keyed                       | D19 | D19 | GND     |  |  |  |  |  |  |

### PC/104-Plus PCI Bus

The PC/104-*Plus* bus is essentially identical to the PCI Bus except for the physical design. A single pin and socket connector is specified for the bus signals. A 120-pin header, CN3, arranged as four 30-pin rows incorporates a full 32-bit, 33MHz PCI Bus. The additional pins on the PC/104-*Plus* connectors are used as ground or key pins. The female sockets on the top of the board enable stacking another PC/104-*Plus* board on top of the Poseidon board.

| A1→ |   |   |   |  |  |   |   |   |  |  |  |   |   |   |  |   |   |

|-----|---|---|---|--|--|---|---|---|--|--|--|---|---|---|--|---|---|

| A1  | H | - | H |  |  | _ | 2 | 2 |  |  |  | _ | = | 2 |  | 4 | _ |

|     |   |   |   |  |  |   | _ | _ |  |  |  |   |   | _ |  |   |   |

|    | Α            | В        | С        | D            |

|----|--------------|----------|----------|--------------|

| 1  | GND/5.0V KEY | Reserved | +5V      | AD00         |

| 2  | VI/O         | AD02     | AD01     | +5V          |

| 3  | AD05         | GND      | AD04     | AD03         |

| 4  | C/BE0*       | AD07     | GND      | AD06         |

| 5  | GND          | AD09     | AD08     | GND          |

| 6  | AD11         | VI/O     | AD10     | M66EN        |

| 7  | AD14         | AD13     | GND      | AD12         |

| 8  | +3.3V        | C/BE1*   | AD15     | +3.3V        |

| 9  | SERR*        | GND      | Reserved | PAR          |

| 10 | GND          | PERR*    | +3.3V    | Reserved     |

| 11 | STOP*        | +3.3V    | LOCK*    | GND          |

| 12 | +3.3V        | TRDY*    | GND      | DESEL*       |

| 13 | FRAME*       | GND      | IRDY*    | +3.3V        |

| 14 | GND          | AD16     | +3.3V    | C/BE2*       |

| 15 | AD18         | +3.3V    | AD17     | GND          |

| 16 | AD21         | AD20     | GND      | AD19         |

| 17 | +3.3V        | AD23     | AD22     | +3.3V        |

| 18 | IDSEL0       | GND      | IDSEL1   | IDSEL2       |

| 19 | AD24         | C/BE3*   | VI/O     | IDSEL3       |

| 20 | GND          | AD26     | AD25     | GND          |

| 21 | AD29         | +5V      | AD28     | AD27         |

| 22 | +5V          | AD30     | GND      | AD31         |

| 23 | REQ0*        | GND      | REQ1*    | VI/O         |

| 24 | GND          | REQ2*    | +5V      | GNT0*        |

| 25 | GNT1*        | VI/O     | GNT2*    | GND          |

| 26 | +5V          | CLK0     | GND      | CLK1         |

| 27 | CLK2         | +5V      | CLK3     | GND          |

| 28 | GND          | INTD*    | +5V      | RST*         |

| 29 | +12V         | INTA*    | INTB*    | INTC*        |

| 30 | -12V         | REQ3*    | GNT3*    | GND/3.3V KEY |

On the Poseidon, all of the PCI circuitry is driven with 3.3V circuitry and is 5V tolerant. The main board can support either 3.3V or 5V-only cards. For this reason, the connector is not keyed (to prevent certain types of cards from being inserted).

# **PS2** Mouse and Keyboard connector

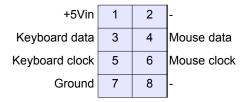

Connector CN19 is a 2x4-pin header used to connect a mouse or keyboard.

| Signal         | Definition          |

|----------------|---------------------|

| +5Vin          | keyboard PS/2 pin 4 |

| Keyboard data  | keyboard PS/2 pin 1 |

| Mouse data     | mouse PS/2 pin 1    |

| Keyboard clock | keyboard PS/2 pin 5 |

| Mouse clock    | mouse PS/2 pin 5    |

| Ground         | PS/2 pin 3          |

# **Utility Connector**

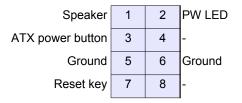

Connector CN18 is a 2/4-pin header for access to the standard button/LED connections.

The following table describes the CN18 connector pinouts.

| Signal           | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speaker          | The signal on the Speaker pin is referenced to +5V out. Connect a speaker between this pin and +5V out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PW LED           | Switched power output to connect a panel power LED. No series resistor is needed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ATX power button | The ATX power button should be tied to ground whenever the "Power Button" is used. The "Power Button" has different functionality, depending on the current system mode and software operation. In general, the following guidelines apply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | • If the board is powered down, toggling (i.e., tie to ground briefly, then release) this button turns the system on, causing all non-standby voltages to become active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  | NOTE: depending on the default configuration, the system usually powers-up immediately as power is applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | <ul> <li>If the system is currently powered up and active, toggling (i.e., tie to ground briefly, then release) this button causes a system power-down event to be initiated. Typically, this powers-down the monitor, hard drive, and any other non-essential functions. The system must be operating and the software executing normally for this function. Under Windows and some other OSs, this power-down event may cause the system to shut down. Typically, this is software-configurable via an option setting for the given OS.</li> <li>If the system is currently powered-up and active, holding this button for four seconds causes a forced system shutdown. This is a hardware power-down, which can be detrimental to many OSs due to the fact that they are not given adequate time to initiate shut-down sequencing. This operation should only be used in critical circumstances, such as when the system itself is locked due to system instability or a software crash. After powering the system down in this manner, the system remains powered down until the power button is toggled (tied to ground again and released).</li> </ul> |

|                  | When ATX is enabled, a momentary contact between this pin and Ground causes the CPU to turn on and a contact of four seconds or longer generates a power shutdown.<br>ATX power control is enabled using a jumper on jumper block JP7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ground           | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Reset key        | Connection between Reset key and ground generate a reset condition. The board remains in a reset state (with non-standby power rails disabled) until Reset key is removed from ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

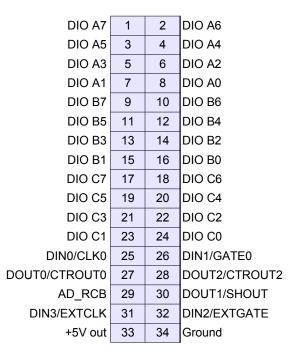

# Data Acquisition (Digital I/O) Connector

Poseidon includes a 2x17-pin header, CN12, for all digital data acquisition I/O.

| Signal    | Definition                                                                        |

|-----------|-----------------------------------------------------------------------------------|

| DIO A7-A0 | Digital I/O port A; programmable direction                                        |

| DIO B7-B0 | Digital I/O port B; programmable direction                                        |

| DIO C7-C0 | Digital I/O port C; programmable direction                                        |

| DIN0-1    | Digital input port with counter/timer and external trigger functions              |

| DOUT0-2   | Digital output port with counter/timer functions                                  |

| CLK0      | Input source to Ctr 0                                                             |

| GATE0     | Pin to control gating of Ctr 0                                                    |

| CROUT0    | Counter 0 output                                                                  |

| CROUT2    | Counter 2 output                                                                  |

| AD_RCB    | A/D convert signal output; can be used to synchronize multiple boards             |

| SHOUT     | -                                                                                 |

| EXTCLK    | External A/D trigger input; Also used for digital interrupt (DINT) input          |

| EXTGATE   | Pin to control gating of Ctrs 1& 2 for A/D timing                                 |

| +5V out   | Connected to switched +5V supply (Output only! Do not connect to external supply) |

| Ground    | Digital ground (0V - reference); used for digital circuitry only                  |

# Data Acquisition (Analog I/O) Connector

Connector CN13 is a 2x20-pin header used for analog I/O data acquisition.

| 2             | Single | -endea | !              |               |    | ential |                |

|---------------|--------|--------|----------------|---------------|----|--------|----------------|

| Vin 0         | 1      | 2      | Vin 16         | Vin 0 +       | 1  | 2      | Vin 0 -        |

| Vin 1         | 3      | 4      | Vin 17         | Vin 1 +       | 3  | 4      | Vin 1 -        |

| Vin 2         | 5      | 6      | Vin 18         | Vin 2 +       | 5  | 6      | Vin 2 -        |

| Vin 3         | 7      | 8      | Vin 19         | Vin 3 +       | 7  | 8      | Vin 3 -        |

| Vin 4         | 9      | 10     | Vin 20         | Vin 4 +       | 9  | 10     | Vin 4 -        |

| Vin 5         | 11     | 12     | Vin 21         | Vin 5 +       | 11 | 12     | Vin 5 -        |

| Vin 6         | 13     | 14     | Vin 22         | Vin 6 +       | 13 | 14     | Vin 6 -        |

| Vin 7         | 15     | 16     | Vin 23         | Vin 7 +       | 15 | 16     | Vin 7 -        |

| Vin 8         | 17     | 18     | Vin 24         | Vin 8 +       | 17 | 18     | Vin 8 -        |

| Vin 9         | 19     | 20     | Vin 25         | Vin 9 +       | 19 | 20     | Vin 9 -        |

| Vin 10        | 21     | 22     | Vin 26         | Vin 10 +      | 21 | 22     | Vin 10 -       |

| Vin 11        | 23     | 24     | Vin 27         | Vin 11 +      | 23 | 24     | Vin 11 -       |

| Vin 12        | 25     | 26     | Vin 28         | Vin 12 +      | 25 | 26     | Vin 12 -       |

| Vin 13        | 27     | 28     | Vin 29         | Vin 13 +      | 27 | 28     | Vin 13 -       |

| Vin 14        | 29     | 30     | Vin 30         | Vin 14 +      | 29 | 30     | Vin 14 -       |

| Vin 15        | 31     | 32     | Vin 31         | Vin 15 +      | 31 | 32     | Vin 15 -       |

| Output ground | 33     | 34     | Vout 0         | Output ground | 33 | 34     | Vout 0         |

| Vout 1        | 35     | 36     | Vout 2         | Vout 1        | 35 | 36     | Vout 2         |

| Vout 3        | 37     | 38     | Analog ground  | Vout 3        | 37 | 38     | Analog ground  |

| DIN3/EXTCLK   | 39     | 40     | Digital ground | DIN3/EXTCLK   | 39 | 40     | Digital ground |

| Signal             | Definition                                                               |

|--------------------|--------------------------------------------------------------------------|

| Vout3-0            | Analog output channels 3 – 0                                             |

| Analog Ground      | 0V analog reference                                                      |

| Vin 31 ~ Vin 0     | Analog input channels 31 – 0 in single-ended mode                        |

| Vin 15 + ~ Vin 0 + | High side of input channels $15 - 0$ in differential mode                |

| Vin 15 - ~ Vin 0 - | Low side of input channels $15 - 0$ in differential mode                 |

| Digital ground     | 0V digital reference                                                     |

| DIN3               | Digital input port with counter/timer and external trigger functions     |

| EXTCLK             | External A/D trigger input; Also used for digital interrupt (DINT) input |

NOTE: The reference grounds are NOT decoupled from the power grounds – they are indirectly connected to the power supply input (and other on-board ground/0V references). Do not assume that these grounds are floating. Do not apply a high-voltage input (relative to the power input ground) to these ground signals or to any other board I/O pin.

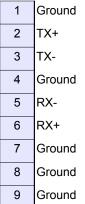

# **Ethernet** Connector

100-gigabit Ethernet connectivity is provided by connectors CN17. Connector CN17 is a 2x5-pin header.

| Common | 1 | 2  | -   |

|--------|---|----|-----|

| DA+    | 3 | 4  | DA- |

| DB+    | 5 | 6  | DB- |

| DC+    | 7 | 8  | DC- |

| DD+    | 9 | 10 | DD- |

| Signal | Definition                        |

|--------|-----------------------------------|

| DA+/-  | Data A; bi-directional pair A+/A- |

| DB+/-  | Data B; bi-directional pair B+/B- |

| DC+/-  | Data C; bi-directional pair C+/C- |

| DD+/-  | Data D; bi-directional pair D+/D- |

### Audio I/O Connector

Connector CN15 is a 2x5-pin header that provides audio connectivity.

| Left headphone/Line out | 1 | 2  | Right headphone/Line out |

|-------------------------|---|----|--------------------------|

| Audio ground            | 3 | 4  | Left line input          |

| Right line input        | 5 | 6  | Audio ground             |

| Microphone input        | 7 | 8  | Power reference          |

| -                       | 9 | 10 | Audio ground             |

| Signal             | Definition                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| Headphone/Line Out | Line Level output, capable of driving headphones, which is referred to<br>as "Headphone Out" in most sound documentation. |

| Line Input         | Line-Level input, which is referred to as "Line In" in most sound documentation.                                          |

| Microphone Input   | Microphone-level mono input; phantom power provided via pin 9.                                                            |

| Power reference    | Microphone power reference                                                                                                |

| Audio ground       | Ground                                                                                                                    |

The Poseidon sound chip is AC97-compatible. The "Line Out" is powered and used for the amplified Speaker Connector output, CN11, described below. The line-level output listed above is listed as either "Headphone Out" or "Line Out 2" in most of the software and documentation for this sound interface.

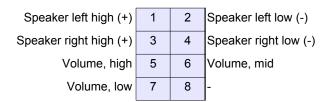

# Speaker Connector

Connector CN11 is a 2x4-pin header used to connect speakers.

| Signal                  | Definition                                                |  |  |

|-------------------------|-----------------------------------------------------------|--|--|

| Speaker LEFT +/-        | Speaker Connection Pair for LEFT speaker (4-Ohm Speaker)  |  |  |

| Speaker RIGHT +/-       | Speaker Connection Pair for RIGHT speaker (4-Ohm Speaker) |  |  |

| Mono Output             | Line-Level mono output (for reference)                    |  |  |

| Volume – LOW, MID, HIGH | These are volume controls for the attached speakers       |  |  |

The volume control is capable of 32 discrete levels, ranging from a 20dB maximum gain to -85dB (Muted). The main volume control is the "MID" line, which may be tied to the center tap of a potentiometer with "HIGH" on one side and "LOW" on the other to give a full range of power control.

- Shorting "MID" to "LOW" mutes the speaker audio.

- Shorting "MID" to "HIGH" provides maximum gain.

- Default (no connection) provides 10dB of gain.

The maximum output power is specified to provide up to two Watts into a 4-Ohm speaker load. Note that this output power is drawn from the on-board 5V supply.

The speakers are driven using a Bridged-Tied Load (BTL) amplifier configuration. This is a differential speaker connection. As such, each speaker should be wired directly to the appropriate pair of connections for that speaker.

- Do not connect the speaker low sides (-) to ground

- Do not short the speaker low connections together.

### **External Auxiliary Power Connector (Output)**

Connector CN10 provides switched power for use with external drives. If ATX is enabled, the power is switched ON and OFF with the ATX input switch. If ATX is not enabled, the power is switched ON and OFF in conjunction with the external power.

| 1 | +5v (switched)  |  |

|---|-----------------|--|

| 2 | Ground          |  |

| 3 | Ground          |  |

| 4 | +12v (switched) |  |

| Signal | Definition                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------|

| +5v    | This is provided by the on-board power supply, derived from the input power. It is switched off when the board is powered down. |

| +12v   | This is provided by the 12V input pin on the main power connector. It is switched off when the board is powered down.           |

| Ground | These are 0V ground references for the power output voltage rails, above.                                                       |

Cable no. 698006 mates with CN15. Thiscable provides a standard full-size power connector for a hard drive or CD-ROM drive and a standard miniature power connector for a floppy drive.

# **IDE** Connector

Connector CN2 is a 2x22-pin header used for the IDE connection.

|         |    |    | _                               |

|---------|----|----|---------------------------------|

| Reset - | 1  | 2  | Ground                          |

| D7      | 3  | 4  | D8                              |

| D6      | 5  | 6  | D9                              |

| D5      | 7  | 8  | D10                             |

| D4      | 9  | 10 | D11                             |

| D3      | 11 | 12 | D12                             |

| D2      | 13 | 14 | D13                             |

| D1      | 15 | 16 | D14                             |

| D0      | 17 | 18 | D15                             |

| Ground  | 19 | 20 | Key (not used)                  |

| DRQ     | 21 | 22 | Ground                          |

| IDEIOW- | 23 | 24 | Ground                          |

| IDEIOR- | 25 | 26 | Ground                          |

| IORDY   | 27 | 28 | Ground                          |

| DACK-   | 29 | 30 | Ground                          |

| IRQ15   | 31 | 32 | Pulled low for 16-bit operation |

| A1      | 33 | 34 | Not used                        |

| A0      | 35 | 36 | A2                              |

| CS1-    | 37 | 38 | CS3-                            |

| LED-    | 39 | 40 | Ground                          |

| +5v     | 41 | 42 | +5v                             |

| Ground  | 43 | 44 | Not used                        |

#### Serial Port I/O Connector

Connector CN20 is a 2x20-pin header that provides access to the four on-board serial ports. The PORT1 and PORT2 serial ports are always configured for RS-232. The PORT3 and PORT4 serial ports are independently, software configurable as either RS-232, RS-485 or RS-422. All four serial ports are independently enabled.

| Port No. | Pin Assignment |

|----------|----------------|

| PORT1    | Pins 1 - 10    |

| PORT2    | Pins 11 - 20   |

| PORT3    | Pins 21 - 30   |

| PORT4    | Pins 31 - 40   |

The following tables list the signals for each mode of operation, including the DE-9 pin numbers associated with the signals.

#### RS-232 Pin Assignment

| COM1: | DCD1 | 1  | 2  | DSR1 |

|-------|------|----|----|------|

|       | RXD1 | 3  | 4  | RTS1 |

|       | TXD1 | 5  | 6  | CTS1 |

|       | DTR1 | 7  | 8  | RI1  |

|       | GND  | 9  | 10 | N/C  |

| COM2: | DCD2 | 11 | 12 | DSR2 |

|       | RXD2 | 13 | 14 | RTS2 |

|       | TXD2 | 15 | 16 | CTS2 |

|       | DTR2 | 17 | 18 | RI2  |

|       | GND  | 19 | 20 | -    |

| COM3: | DCD3 | 21 | 22 | DSR3 |

|       | RXD3 | 23 | 24 | RTS3 |

|       | TXD3 | 25 | 26 | СТЅЗ |

|       | DTR3 | 27 | 28 | RI3  |

|       | GND  | 29 | 30 | N/C  |

| COM4: | DCD4 | 31 | 32 | DSR4 |

|       | RXD4 | 33 | 34 | RTS4 |

|       | TXD4 | 35 | 36 | CTS4 |

|       | DTR4 | 37 | 38 | RI4  |

|       | GND  | 39 | 40 | ]-   |

| Signal | Definition          | DE-9 Pin | Direction |

|--------|---------------------|----------|-----------|

| DCDn   | Data Carrier Detect | pin 1    | Input     |

| DSRn   | Data Set Ready      | pin 6    | Input     |

| RXDn   | Receive Data        | pin 2    | Input     |

| RTSn   | Request to Send     | pin 7    | Output    |

| TXDn   | Transmit Data       | pin 3    | Output    |

| CTSn   | Clear to Send       | pin 8    | Input     |

| DTRn   | Data Terminal Ready | pin 4    | Output    |

| RIn    | Ring Indicator      | pin 9    | Input     |

| GND    | Ground              | -        | -         |

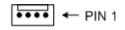

# RS-485 Pin Assignment

Only CN20 connector pins 21 through 40, PORT3 and PORT4, are used for RS-485.

| Signal    | Definition                           | DE-9 Pin | Direction      |

|-----------|--------------------------------------|----------|----------------|

| TXD/RXD+n | Differential Transceiver Data (HIGH) | pin 2    | bi-directional |

| TXD/RXD-n | Differential Transceiver Data (LOW)  | pin 7    | bi-directional |

| GND       | Ground                               | -        | -              |

| NC        | (not connected)                      | -        | -              |

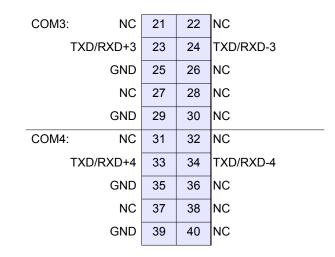

# **RS-422** Pin Assignment

Only CN20 connector pins 21 through 40, PORT3 and PORT4, are used for RS-422.

| Signal      | Definition                 | DE-9 Pin | Direction |

|-------------|----------------------------|----------|-----------|

| TXD+n/TXD-n | Differential transmit data | -        | Output    |

| RXD+n/RXD-n | Differential receive data  | -        | Input     |

| GND         | Ground                     | -        | -         |

| NC          | (not connected)            | -        | -         |

#### **External Battery Connector**

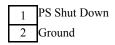

Connector CN8 is used to connect an external battery. The battery voltage for this input should be 3-3.5V. The current draw averages under  $4\mu$ A at 3V.